AD9226 芯片功能与使用方式简记

AD9226是一款单芯片、12位、65 MSPS模数转换器(ADC),采用单电源供电,内置一个片内高性能采样保持放大器和基准电压源。它采用多级差分流水线架构,数据速率达65 MSPS,在整个工作温度范围内保证无失码。

——摘自 ADI网站

常用参数

- 最大速率:65 MSPS

- 位数:12 bit

- 供电方式:单电源 5V(0.25V 容差)

- 输出逻辑电平兼容性:3.3V & 5V

- 量程:0~2*VREF(上限不超过 AVDD)

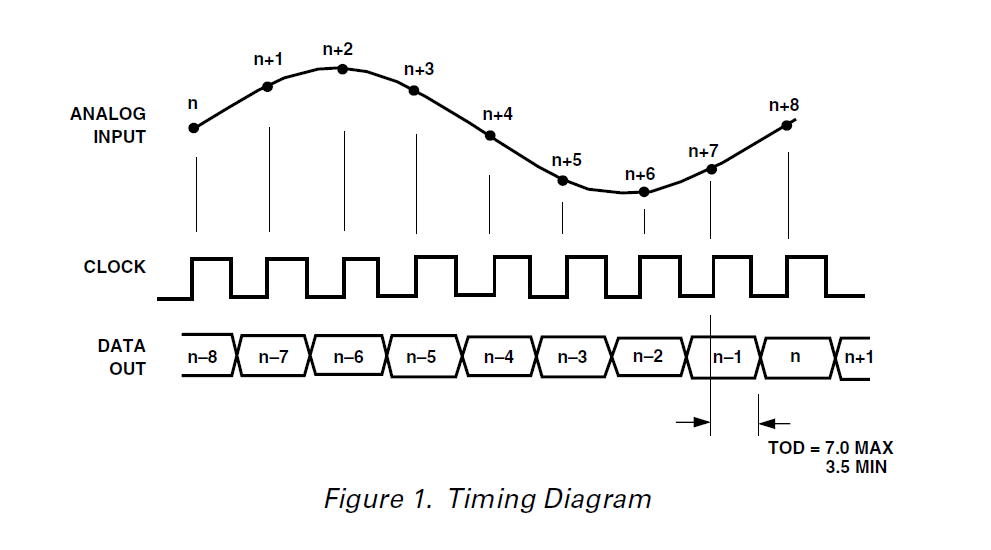

时序图

可见,在时钟上升沿时读取数据即可。 另:对于前 8 个时钟上升沿所读取到的数据应当予以丢弃。

引脚功能

以下说明基于 LQFP 封装。

DRVDD & DRVSS 引脚

逻辑电平参考引脚。

控制输出端数字逻辑电平的值。

SENSE 引脚

VERF 选择引脚。

- 接 AVSS:VREF 接入内部参考电位,2.0V。

- 与 VREF 短接或通过电阻连接:VREF 接入内部参考电位,1.0V。 也可通过电阻网络配置 1.0V~2.0V 之间的电位。

- 接 AVDD:VREF 使用外部参考。

OEB 引脚

输出使能引脚。

- 接 AVSS:三态门导通。

- 接 AVDD:三态门为高阻态。

MODE2(DFS)引脚(Pin 35)

输出数据格式选择引脚。

- 接 AVSS:输出为二进制原码

- 接 AVDD:输出为二进制补码

MODE1(CSF)引脚(Pin 43)

时钟稳定器控制引脚。

- 接 AVSS:关闭时钟稳定器

- 接 AVDD:开启时钟稳定器

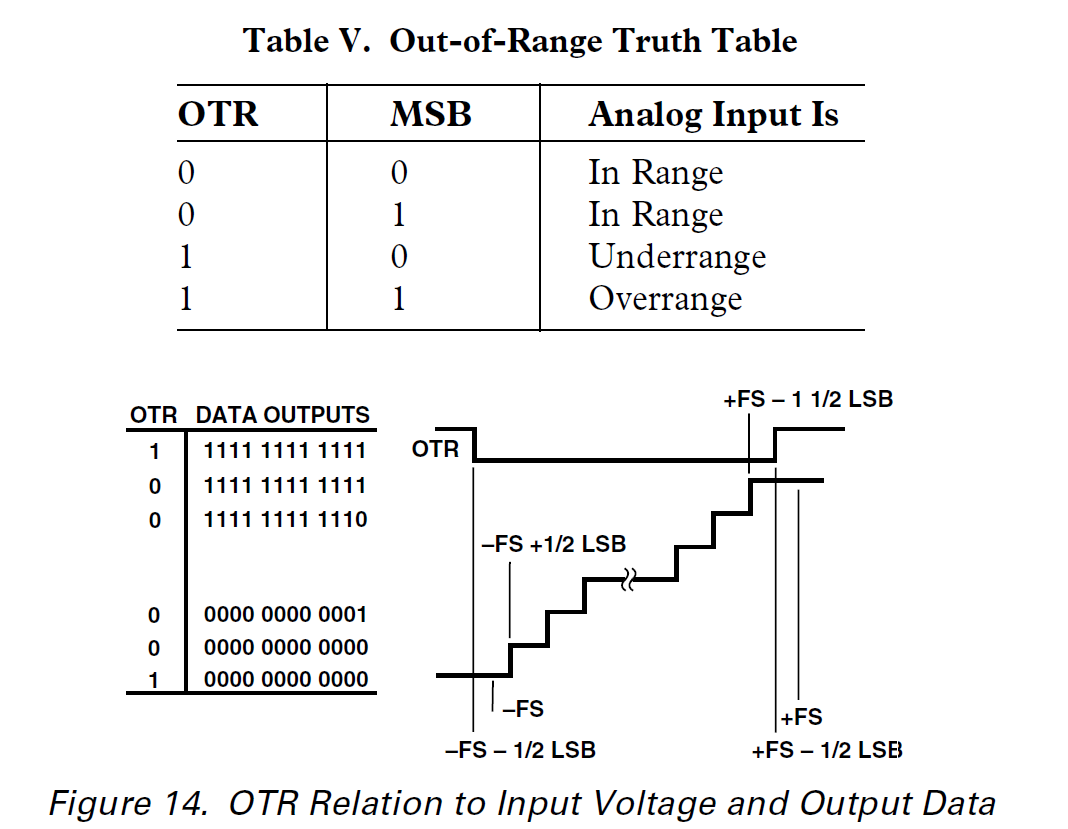

OTR 引脚

模拟输入超量程标志。

- 高电平:表明模拟输入的信号超过量程。

- 该标志位可以为增益控制提供反馈。

- 配合 MSB 可得到更详细的超量程信息。

其他

- AD9226 的超高带宽在某些噪声敏感的应用场景内可能会带来负面影响。可以采取引入 RC 低通滤波器的方式来进行改善。此外,应做好 VINA、VINB 的阻抗匹配。

- 高速 ADC 对时钟质量要求较高。应避免时钟信号与数字信号相互干扰。最好用低噪声晶振作为时钟源。

- AD9226 芯片上的 BIT1 是 MSB,而 BIT12 是 LSB,这与通常的习惯不太一样。

- (以实际情况为准)在某些成品模块中,AD 芯片上的输入电压 $ V_{AD} $ 和 PCB 上的输入电压 $ V_{IN} $ 具有如下关系: \[ V_{AD}=2+0.2V_{IN} \] e.g. PCB 上的输入为 5V 时,AD 上的输入为 3V ;PCB 上的输入为 -5V 时,AD 上的输入为 1V。