对 2023 电赛 H 题《信号分离装置》的一些思考

2023,电赛落幕。

回顾比赛,总是是紧张而匆忙的,H题看似人畜无害,但“同频同相”显示暗藏玄机,一度成为最大的瓶颈。在比赛期间,也是大大小小的挫折不断(感觉全年的坏运气都集中在那几天了)。最后,因为一些评审方面的原因,与国奖擦肩而过,非常意难平。

在赛后,方得以有时间再次思考。回顾了一下作品,有一些心得,在此分享一下,也算是给两年来电赛的风风雨雨画上个句号吧。

赛题回顾

原题位置:https://res.nuedc-training.com.cn/topic/2023/topic_102.html

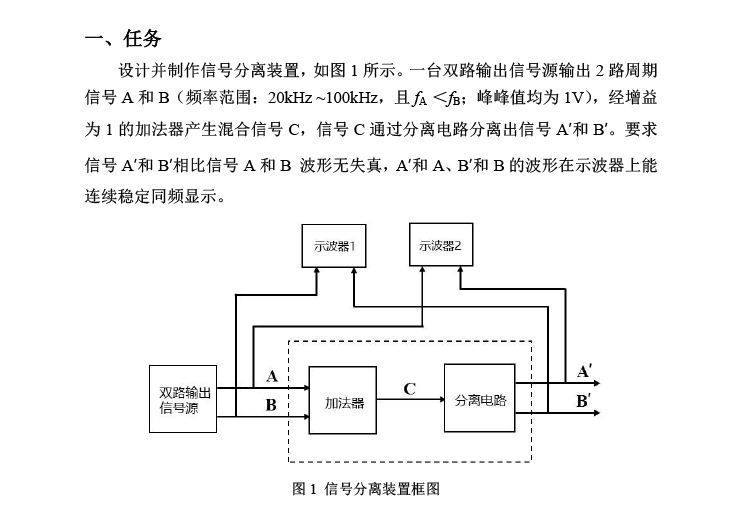

简单概括一下,就是:

- 组委会随机给出两组输入信号,可能是三角波或正弦波,频率为

20k~100kHz,步进为5kHz,且频率B是A的整数倍,波形峰峰值不小于 `1V。 - 我们需要设计加法器,自行将两个信号混合,并将混合信号输入进分离电路中。注意,原始信号和分离电路之间不能有任何连接。(否则就没意思了)

- 分离后的信号称为

A'和B',需要将其与原始信号A和B同时同频稳定显示在示波器上,即以其中一路为触发源时,另一路波形要无漂移。

技术路线

路线一

滤波 - 放大法。

主要架构

混合信号 -> ADC -> FFT -> 波形识别与频率分析

混合信号 ---选通---> 多个不同频段的 FIR --> 输出

以此方案实现,需要多个 FIR 带通滤波器,将它们设定在不同频率下。根据波形分析结果,可以选择对应的滤波器,直接分离出信号。

对于 FIR 系数的设计,在 MATLAB 工具的辅助下,工作量尚可。此方案的好处是能很好地实现“同频显示”,输出信号是由混合信号滤波而来,不存在频率偏移问题。

但是,5kHz 的带宽要求较窄,设计出的滤波器的阶数较高,而且在定点化后,经测试,滤波效果不是很理想,分离出的波形会有另一个波的残余。采用更高阶数确实能有改善,但加上后来 FFT 的 Verilog 设计后,可能有些问题,实例化多个 FIR 后综合器每次综合都要十几分钟,有时还报错,因此只能放弃这个方案。

不选用此方法的另一个原因在于,题目要求控制输出信号的相位差,如果采用滤波法,那么相位控制可能有困难。(我当时的设想是用硬件移相,而不是软件处理,效果一般)。如果有什么好办法,欢迎你留言讨论。

路线二

分析 - 重建法。

主要架构

混合信号 -> ADC -> FFT -> 波形识别与频率分析

混合信号、重建信号 -> 鉴相 -> 控制 DDS 频率控制字

此方法的思想是,首先通过 ADC 采样混合信号,并进行 FFT 分析,得到混合信号的成分(波形类型与频率)。

根据分析得出的信息,可以控制 DDS 产生出相应的信号。

波形识别

波形识别方面用 FFT 自然不必多说。但这里有个识别方案上的小细节:

我们都知道,三角波具有多条谱线,而正弦波是单谱线,因此可以依据这个进行波形识别。但仔细一想,事情没有那么简单,在特定的组合下,正弦波的基波可能和三角波的谐波正好处于同一位置,存在混叠。因此需要分类讨论进行甄别。实践起来,这个方法还是比较复杂的(正弦波恰好是三角波的3倍频?三角波恰好是正弦的3倍频?),实际使用过程中也有一定的误判率。

从另一个角度入手就简单了不少。注意到,题设给出,此次输入的三角波和正弦波的幅度都是1V。我们可以利用这个条件——对于等幅波形输入,FFT变换后的频谱上,三角波的基波的幅值小于正弦波的基波幅值。这是很好理解的,从数学上可以严格证明,但这里提供一个直观的思路:正弦波的能量全部集中在基波里,而三角波的能量从基波中还要拿出一部分,分配给各次谐波。

这是一条重要的依据,以幅值入手进行判决,就简单了不少:找到频谱中最大值所在的频率,此处就是正弦波的频率,次大值对应的就是三角波。

那不用管频谱混叠吗?确实不用管。你可以试着想一想,就算混叠了,对判断结果也没有影响,不是吗?正弦波叠加了三角波的谐波,只会更大,它仍是频谱上的最大值;而三角波的基波,永远是次大值。

信号重建

在信号重建部分,难点出现了——“同频稳定显示”。

最初的设想是, 测出原始信号的频率,然后通过控制 DDS 生成一路同频信号。但经过测试,除非两个信号的频率差达到小数点后4~5位,否则都会有肉眼可见的漂移。原因有:一方面,要测出如此高精度的频率是困难的;另一方面,在重建时,由于器件性能的差异,实际生成的波形频率和理论值之间也存在误差,造成了频率的不确定性。

一些队伍也尝试在提高精度方面进行了努力,包括:

- 更换硬件 DDS 发生器上的晶振(降频),以提升频率分辨率;

- 如果是 FPGA 实现的 DDS,则增加控制字的位宽(此方法控制上更灵活)。

这些方法确实能做到提升,虽然有效但非常有限。

深入地看,造成频率偏差的本质原因,在于这种简单重建方案割断了“原始信号”与“恢复信号”之间的联系,可以说二者之间并不相关。试想,两个信号并没有一个共同的“基准”。

原始信号的产生,频率参考是基于外部的信号源的晶振;而重建信号的频率参考,是我们 DDS 硬件的晶振。只有两个晶振完全相同,且我们的控制参数也设置得完全相同 ,那么理论上才可能产生出完全同频的波形。这在现实生活中是不可能的。

引入反馈

所以,要想稳定显示,更进一步的思想是,引入“反馈”。在鉴频鉴相中, 我想到了两种方案,一软一硬。

硬件上的方案是使用一个锁相放大器,AD630,大致的原理是,他会将参考信号与被测信号相乘,随后通过一个LPF,得到“直流电平”,电位高低反映了相位差的大小。具体的原理可以参考网上资料,也可以查看《新概念模拟电路》这一本书。在实际使用过程中,如果两个信号频率很接近,那么输出的“直流电平”实际是一个很低频的正弦信号,此信号的频率为两路信号的频率差。根据频率差的大小,调整DDS的控制字即可逐渐减小误差。

FPGA 的软方案,是指采用数字鉴相器进行实现,在 ADC 采样得到的数据中直接进行分析比较即可。这一方案应该更好,但由于没有此方面的经验,比赛时还是采用了第一种硬方案。

注意,我推荐的 FPGA 方案是鉴相而不是鉴频。我们比赛时用的鉴频法有一个潜在问题,即,当重建信号频率很接近目标时,频率差很小,在 0.1Hz 以下。这就导致输出的频率差信号自身频率很低,对其进行测量时,至少要等待两个过零点,这会非常的慢(5s),很容易超时。因此,推荐使用鉴相的方式进行,比如 CORDIC 算法,或者同时以较高速率采样两路信号,直接比较过零点的时刻,得到时间差,然后再将信息转化为 DDS 的控制字。

有能力的同学还可以尝试引入 PID 之类的控制算法,我本身是做信号题和高频通信题出身,而今年的赛题和往年风格不太相同,准备的很多东西没用上,因此这方面也有所欠缺,也算是个造成遗憾的原因吧。

其他

在鉴频方面,有一个有意思的地方值得一提,由于信号频率都是 5kHz 的整数倍,因此采样频率设定为 5kHz,根据数字信号处理的知识,这能够直接测量出频率差:

- 如果信号频率等于采样频率,采样后得到的信号会是一个直流信号,因为在每个采样点上,信号的值是相同的。

- 如果信号频率是采样频率的整数倍(如 10kHz、15kHz 等),采样后信号的高频部分会折叠到低频部分,导致混叠,但由于是严格整数倍,频谱移动后能够与 5kHz 完全重合,这种情况下采到的也是直流

- 那么,如果频率存在一个微小的偏移,例如 15.1kHz,以 5kHz 采样,就会得到一个 100Hz 的正弦波,这样就测出了信号与采样频率之间的差值。

文章推荐

另外,强烈推荐阅读:2023年电赛H题[信号分离装置]小论

后记

虽然没有取得预期的成绩,但无论是备赛还是竞赛,自己在各方面的能力也都得到了锻炼,总的来说,收获还是很丰富的。回过头看,有苦有乐,有得有失,或许这就是常态。

感谢我的两位队友,也感谢读到这里的你。希望上面的一点心得能带给大家帮助,也欢迎在下方评论分享更好的做法。在此与诸君共勉,愿各位都能前程朗朗。